| |

|

НПО Системы Безопасности (499)340-94-73 График работы: ПН-ПТ: 10:00-19:00 СБ-ВС: выходной  |

Главная » Периодика » Безопасность 0 ... 121122123124125126127 ... 233 Пример сессии разработки проекта на базе ПЛИС в этом разделе приводятся пошаговые инструкции для разработки ПЛИС устройств. Здесь показано, как выполнить проектирование одного устройства двумя разными способами: посредством разработки принципиальной схемы и CUPL кода. Также приведены рекомендации по созданию исходного файла для процесса моделирования и сам процесс моделирования ПЛИС устройств. Этапы разработки Проверка технического задания Для начала рекомендуется тщательно изучить поставленную задачу. Следует помнить, что устройство может быть спроектировано либо посредством создания принципиальной схемы (рис. 5.19), либо посредством описания на языке CUPL. При выборе описания на языке CUPL главными инструментами проектирования будут конечные автоматы, булевы уравнения и таблицы истинности. Надо попытаться определить, какой тип синтаксиса наилучшим образом подходит для выполнения данной задачи. Создание исходного файла для компилятора Для создания исходных файлов рекомендуется использовать входящие в комплект поставки файлы шаблонов, где следует удалить ненужные секции. Далее требуется отредактировать заголовок файла таким образом, чтобы он отражал содержимое нового проекта. Составление выражений Для правильного описания требуемой логической схемы необходимо составить выражения, пользуясь синтаксическими правилами языка CUPL. Вьфажения могут быть записаны в булевом формате, в виде конечных автоматов или как таблица истинности. Выбор целевого устройства При выборе целевой микросхемы следует убедиться, что выбранное устройство имеет достаточное число входных выводов. Проверьте также наличие достаточного количества буферизованных и небуферизованных выходных выводов. При необходимости убедитесь в наличии выводов управления с тремя состояниями. Следует также проверить, может ли устройство адекватно управлять требуемым количеством комбинационных логических блоков. Выбор целевой микросхемы осуществляется в диалоговом окне Configure PLD. Распределение выводов Далее следует корректно распределить входы и выходы проекта между выводами целевого устройства. Делать это надо исходя не только из оптимальной реализации логической схемы, но и с учетом того, что конечное устройство будет располагаться на печатной плате и соединяться с другими компонентами. Используя предоставляемые производителем справочные материалы, необходимо проверить правильность функционирования выбранного устройства. Подготовка к компилированию Определите, какие форматы файлов будут необходимы для загрузки схемы и моделирования, а также какой минимизатор вам понадобится. Теперь все готово для компиляции проекта. RESET сри.ак IMEMB. тш риз READY ВИ1 А О А о RflV --RAM2 А О RflV Рис. 5.19. Микропроцессорная система на базе ПЛИС Шаг 1 - проверка технического задания в этом примере ПЛИС обеспечивает гибкий интерфейс между процессором и периферийными устройствами, выполняя функции временного управления и декодирования адреса для получения сигнала выбора микросхемы CS. Карта памяти, приведенная на рис. 5.20, показывает, где в адресном пространстве процессора находятся микросхемы ПЗУ и ОЗУ. ПЛИС будет декодировать эти диапазоны адресов для генерирования та асп еделения сигнала выбора соответствующей микросхемы. памяти Приведенная таблица 5.34 создается на основе карты памяти, изображенной на рисунке слева, где адреса показаны в шестнадцатеричной форме. В ней показано состояние адресных линий для каждого диапазона декодируемых адресов. Из таблицы следует, что ПЛИС должна в качестве входов использовать адресные линии А11 - А15. Таблица 5.34

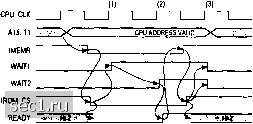

Вследствие малого быстродействия микросхем ПЗУ, ПЛИС должна также уметь генерировать циклы ожидания при обращении процессора к этим микросхемам. Взаимосвязь различных сигналов на временной диаграмме (рис. 5.21) показана стрелками. Числа в скобках показывают номер положительного перепада тактового сигнала (CLOCK).  Рис. 5.21. Временные диаграммы сигналов Wait Последовательность циклов ожидания начинается после установки правильного адреса и продолжается до строба чтения памяти. Необходимо рассмотреть только сигнал 1MEMR, так как циклы ожидания генерируются только для ПЗУ. Когда строб 1MEMR активен для адреса, соответствующего области ПЗУ, генерируется сигнал lROM CS, и буфер с тремя состояниями переключается в логический "О", что приводит к подаче низкого уровня на вывод READY процессора (это означает перевод процессора в состояние ожидания). Следующий положительный перепад тактового сигнала (1), идущий уже после !ROM CS, устанавливает сигнал WAIT1. Далее после прохождения одного целого тактового периода по положительному перепаду тактового сигнала (2) устанавливается сигнал WAIT2, а период цикла ожидания (один такт процессора) завершается, что приводит к установке сигнала READY в положение логической "1". Это заставляет процессор продолжить цикл чтения путем сброса строба IMEMR. Далее сбрасывается сигнал IROM CS, который устанавливает буфер в высокоомное Z-состояние, что приводит к сбросу сигналов WAIT1 и WAIT2 по следующему положительному перепаду тактового сигнала (3). Теперь генератор циклов ожидания готов для следующего обращения процессора. Шаг 2 - создание исходного кода на языке CUPL На этом шаге создается файл логического описания проекта на базе ПЛИС. Этот файл пишется на языке описания логических схем CUPL и является входным для компилятора, который, обработав его, создает файл для загрузки в программатор. Создание заголовочной секции исходного файла проекта на базе ПЛИС приведено ниже. Следующая за заголовком секция - титульный блок, который в действительности содержит обычные комментарии, обрамленные наборами символов "/*" и "*/". В титульном блоке приводится краткая информация, описывающая данный проект. WAITGEN.PLD Name Partno Date Revision Designer Company Assembly Location Device WaitGen; P9000183; 07/16/87; 02; Osann; ATI; PC Memory; U106; ; /* the device is selected later */ 0 ... 121122123124125126127 ... 233 |