| |

|

НПО Системы Безопасности (499)340-94-73 График работы: ПН-ПТ: 10:00-19:00 СБ-ВС: выходной  |

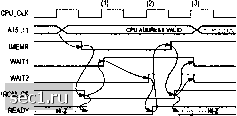

Главная » Периодика » Безопасность 0 ... 124125126127128129130 ... 233 Логическая схема генерации сигнала выбора микросхемы Существует большое количество способов построения логической схемы генерации сигнала выбора микросхемы. Приводимый пример использует наиболее простой для понимания способ. Обратимся к таблице 5.34, где показано состояние адресных линий для каждого сигнала выбора микросхемы, который генерируется ПЛИС. Используя информацию из таблицы 5.34 и схемы, приведенной на рис. 5.19, можно написать следующие основные вьфажения: ROM CS = !А15 & !А14 & А13 & IMEMR RAM CSO = !А15 & !А14 & А13 & !А12 & !А11 & (IMEMR # IMEMW) RAM CS1 = !A15 & !A14 & A13 & !A12 & All & (IMEMR # IMEMW) Невозможно реализовать выражения для выбора микросхем ОЗУ, поскольку они содержат и логическое умножение (AND), и логическое сложение (OR), поэтому нужно сначала создать промежуточные сигналы. Из таблицы 5.34 видно, что все сигналы выбора MHiqrocxeM требуют логического нуля на А15 и А14. Они могут быть объединены с помощью библиотечного элемента AND2B2: ADR 15 14 = !А15 & !А14 (ADR 15 14 вырабатывается, когда и А15, и А14 имеют логический "О"). Сигналы выбора микросхем ОЗУ требуют логической "1" на А13 и логического "О" на А12. Поэтому эти сигналы могут быть объединены с помощью элемента AND2B1: ADR 13 12 = !А13 й А12 (ADR 13 12 вырабатывается, когда А13 в "1", а А12 в "О"). Сигналы чтения и записи в память также могут быть использованы для создания промежуточной переменной запроса памяти, которая будет входить в выражения для выработки сигналов выбора микросхем ОЗУ. Их можно объединить посредством элемента OR2B2: MEMREQ = IMEMR Sc IMEMW (MEMREQ вырабатывается, когда либо MEMR, либо MEMW устанавливается в "О"). Теперь эти промежуточные сигналы могут быть объединены с другими адресными линиями для создания трех сигналов выбора микросхемы. Получившаяся схема приведена на рис. 5.25. f>-L г-О- > nand4 > -i-1- Рис. 5.25. Схема выбора микросхемы памяти Логическая схема для генерации циклов ожидания Для описания логической схемы генерации циклов ожидания необходимо обратиться к временной диаграмме, представленной на рис. 5.26.  Рос. 5.26. Временные диаграммы формирования сигналов Wait Сигнал WAIT1, выставляемый по ближайшему фронту тактовых импульсов, требуется в качестве ответа на подачу сигнала ROM CS. Прежде чем реализовать на D-триггере схему выдачи этого сигнала, заметим, что, как показано на системной диаграмме, схема на ПЛИС должна сбрасываться по сигналу RESET процессора. Сброс с активным высоким уровнем может быть включен в состав генератора циклов ожидания посредством операции логического умножения (AND) с ROM Ci5. Получим следующее выражение: START WAIT = !ROM CS & !RESET ; Генератор циклов ожидания должен обеспечить пассивное положение сигнала READY в течение, по крайней мере, одного тактового интервала. WAIT1 станет активным по первому положительному перепаду тактового сигнала процессора после выдачи ROM CS, поэтому теперь нужно сгенерировать сигнал по второму тактовому импульсу. Этого можно достичь, подав сигнал с выхода первого D-триггера на D-вход второго. Второй триггер сработает по второму тактовому импульсу. Это и будет сигнал WAIT2. По временной диаграмме видно, что сигнал READY, приходящий на процессор, после завершения операции доступа к ПЗУ должен вернуться в третье высокоомное состояние. Для этого необходимо использовать буфер с тремя состояниями, разрешением выхода которого управляет сигнал ROM CS. Схема, представленная на рис. 5.27, демонстрирует данную реализацию генератора циклов ожидания. AN02B2 U1CI BUFT ROM CS Рис. 5.27. Схема формирования сигналов ожидания Связь внутренней логической схемы с выводами компонента Последним этапом здесь является задание связей внутреиией логической схемы с физическими выводами микросхемы. Для этого в библиотеке символов существуют специальные символы контактов - IPAD, OPAD иЮРАО. Эти символы размещаются в местах соединения схемы с физическими выводами компонента. Количество выводов, подсоединяемых к данному символу контакта, указывается в его поле Part Field 1 и имеет следующий синтаксис: LOC=PIN[pin number] После размещения соответствзоощих символов контактов и их нумерации согласно выбранному целевому устройству полная схема будет выглядеть, как показано карие. 5.28. Д11 utoo START VWT 1" BUFT Jj£MR£ -Ш55- R2tL££ > NANCM ADR 12 13 U12 OPAD LOC-PIHIIS LOC>nHtt4 Puc. 5.28. Окончательная схема устройства Замечания Законченный проект компилируется так же, как и в случае описания его на языке CUPL (см. шаг 6 - компиляция исходного файла). Вся внутренняя логическая схема должна иметь уникальные позиционные обозначения, однако специальных требований на них не накладывается. Присваивание имен всем внутренним цепям может значительно облегчить отладку устройства. 0 ... 124125126127128129130 ... 233 |