| |

|

НПО Системы Безопасности (499)340-94-73 График работы: ПН-ПТ: 10:00-19:00 СБ-ВС: выходной  |

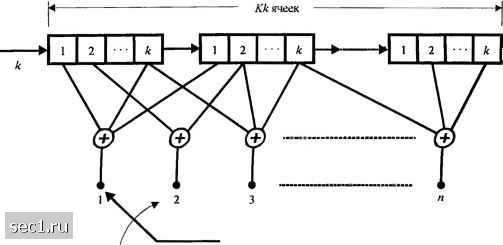

Главная » Периодика » Безопасность 0 ... 127128129130131132133 ... 262 характеризуемых многопутёвостью и замираниями, которые в подробностях описаны в главе 14. Замирания сигнала, обусловленные меняющимся во времени многопутевым распространением волн, часто вызывают снижение уровня сигнала ниже уровня шума, что приводит к большому числу ошибок. Второй пример это класс каналов магнитной записи (ленточной или дисковой), в которых дефекты в записывающей среде приводят к пачкам ошибок. Такие группы ошибок обычно не исправляются кодами, оптимально рассчитанными для статистически независимых ошибок. Значительные работы были выполнены по синтезу кодов, которые способны исправить пакеты ошибок. Вероятно, наиболее известными кодами, исправляющими пакеты ошибок, является подкласс циклических кодов, называемых кодами Файра, в честь П.Файра (1959), который их открыл. Другой класс циклических кодов для исправления пакетов ошибок был позднее открыт Буртоном (1969). Пакет ошибок длины h определяется как последовательность из b символов (бит) ошибок, первым и последним из которых является «1». Способность кода исправить пачки оитбок определяется длиной наиболее короткой пачки ошибок, которую он не может исправить. Относительно просто можно показать, что систематический {п,к) код, который имеет п к проверочных символов, может корректировать пачки ошибок длиной h<\\{n к)\. Эффективный метод работы в каналах с пачками ошибок заключается в перемежении кодовых посылок таким путём, что канал с пачками ошибок трансформируется в канал, имеющий независимые ошибки. Затем используется код, рассчитанный на независимые ошибки в канале (короткие пакеты). Блок-схема системы связи, которая использует перемежение символов, показана на рис. 8.1.20. Входные данные Кодер канала Псрсмежитель Модулятор Канал Выходные дгипые Декодс!) канала Денеремежитель Демодулятор Рис. 8.1.20. Блок-схема системы связи, использующей перемежение в канале с фуппированием ошибок Кодированные данные перегруппируются перемежителем и передаются по каналу. На приёме, после (жёстких или мягких решений) демодулятора денеремежитель восстанавливает символы в нужной последовательности и направляет их к декодеру. Как результат перемежения-деперемежения, пачки ошибок рассеиваются во времени так, что ошибки внутри кодовых слов становятся независимыми. Перемежитель может принять одну из двух форм: блоковая структура или свёрточная структура. Блоковый перемежитель формирует кодированные данные в прямоугольный массив из т строк и столбцов. Обычно, каждая строка массива состоит из кодового слова длин . Перемежитель степени т состоит из т столбцов (w кодовых слов) как показано на рис. 8.1.21. Счктипание h;j.\hJiiiij\ бнг в модулятс») t t t t t t

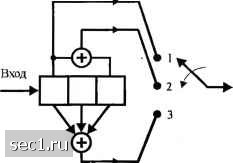

Рис. 8.1.21. Псремеио1тель кодированны.ч бит Биты считываются по столбцам и передаются по каналу. В приёмнике деперемежитель располагает данные в тот же прямоугольный формат, но теперь они считываются по строкам, одно кодовое слово за раз. Результат такой перегруппировки данных при передаче по каналу сводится к тому, что пачка ошибок длины I - nib разбивается на т пачек длиной h каждая. Таким образом, код {п,к), который может справляться с пачкой ошибок длины b < \ \{п к)\ можно соединить с перемежителем степени /;/ для того. чтобы образовывать блоковый код (iiin,fnk), который может справляться с пачками ошибок длиной I = mh. Сбсрпючпып перемежитель можно использовать вместо блокового перемежителя таким же путём. Свёрточные перемежители лучше согласованы к использованию совместно со свёрточными кодами, которые описываются в следующем разделе. Структура свёрточного перемежителя была описана Рамсеем (1970) и Форни (1971). 8.2. СВЁРТОЧНЫЕ КОДЫ Свёрточный код создаётся прохождением передаваемой информационной последовательности через линейный сдвиговый регистр с конечным числом состояний. В общем, регистр сдвига состоит из К (А-битовых) ячеек и линейного преобразователя, состоящего из функциональных генераторов и выполняющего алгебраические функции, как показано на рис. 8.2.1. Входные данные к кодеру, которые считаются двоичными, продвигаются вдоль регистра сдвига по к бит за раз. Число выходных битов для каждой А-битовой входной последовательности равно . Следовательно, кодовая скорость, определённая как - к/п. согласуется с определением скорости блокового кода. Параметр К назьшается кодовым ограничением свёрточного кода. Чаще всего при А-=1 кодовым офаничснием называют число А.-1 (прп) " Во многи.ч слл-чая.ч кодовое офаничение кода задается скорее в битах, чем в А-битовых блоках. Следовательно, регистр сдвига моукно назвать £,-ячссчным регистром сдвига, где L Кк . Более того, в общем сл>час L может и не быть кратным К. информационных бит  Кодированная последовательность (к модулятору) Рис. 8.2.1. Свёрточный юдер Один метод для описания сверточного кода сводится к заданию его порождающей матрицы, так же, как мы это делали для блоковых кодов. В общем, порождающая матрица для сверточного кода полубесконечная, поскольку входная последовательность полубесконечная. Можно использовать эквивалентное представление кода, в котором мы определяем набор из « векторов, один вектор для каждого из п сумматоров по modi. Каждый вектор имеет Кк измерений и содержит в себе информацию о соединениях кодера с сумматорами по mod 2. «1» в /-ой позиции вектора указывает на то, что соответствующая ячейка регистра сдвига подсоединена к сумматору по mod 2, а О в данной позиции указывает на то, что такого соединения нет. Для конкретности рассмотрим двоичный свёрточный кодер с кодовым ограничением К = 3, к = 1 н ы = 3, показанный на рис. 8.2.2.  Выход  Рис. 8.2.2. Свёрточный кодер с А=3, Icl, и-3 Считается, что первоначально все ячейки регистра сдвига находятся в нулевом состоянии. Допустим, что первый входной бит «1». Он без задержки появляется на выходе первой (левой) ячейки регистра и, соответственно, на всех трёх входах выходного ключа (мультиплексора). Ключ поочерёдно вьщаёт содержимое входов, и выходная последовательность из 3 бит 111. Допустим, что второй входной бит «О». Он записывается в первую ячейку регистра, проталкивает предыдущий бит («1») во вторую ячейку - и на входах мультиплексора (сверху вниз) появляются О, О и 1. Тогда вторая выходная последовательность 001. Если третий входной бит 1, выходная последовательность 100 - и так далее. Таким образом, в ответ на каждый входной бит ( = 1) свёрточный кодер 0 ... 127128129130131132133 ... 262 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||